SDRAM Contoller Chisel Generator

Final project for CSE 228A - Agile Hardware Design

Introduction

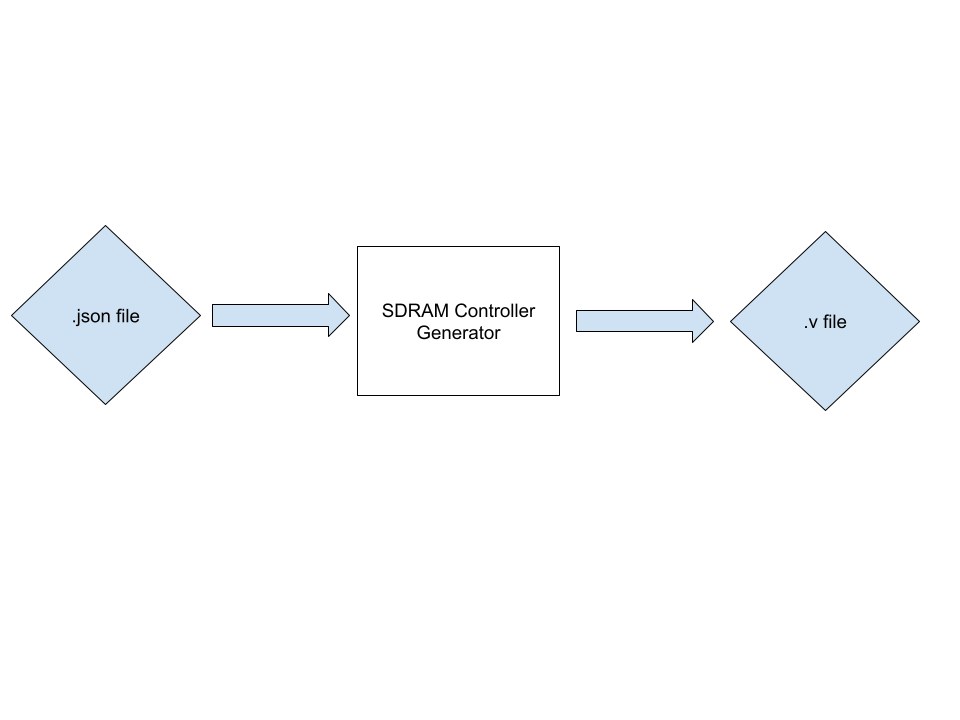

The goal of this project is to take in a JSON file describing timing characteristics of a SDRAM module and generating a Verilog file describing the desired controller module for use on an FPGA or tapeout for an ASIC. Below is the dataflow of the generator from JSON to Verilog.

A hardware generator language here is used rather than a hardware description language due to flexiblity. Verilog would create a single instance of an SDRAM controller and would be rigid if any changes are needed for the controller or someone else would like to reuse it for a different SDRAM module. My project aims at providing hobbyists a program that just needs them to write down key values from their SDRAM’s datasheet to generate a controller for them to use.

This is an open source Scala project and contributions are welcome! Visit the repo at: https://github.com/gmejiamtz/sdram_controller_generator

Future Work

Below is a list of future work for the project to take off for my liking:

-

Get Data Transfer to work properly - Chisel Analog is not as mature as Verilog’s inout and is causing me problems in data movement to and from the SDRAM via the controller

-

Target more SDRAMs - as of now I am targetting only the Micron MT48LC1M16A1 and I believe different SDRAMs have different initialization procedures and command formats

-

Create a JSON template and parser front-end - will be a future assignment as this is fairly easy to parse but the template will take time